# UNIVERSITY OF CALIFORNIA Los Angeles

Prove Once, Run Efficiently Anywhere:

Tools for Lock-free Concurrent Algorithms

A dissertation submitted in partial satisfaction of the requirements for the degree Doctor of Philosophy in Computer Science

by

John Bender

#### ABSTRACT OF THE DISSERTATION

Prove Once, Run Efficiently Anywhere: Tools for Lock-free Concurrent Algorithms

by

John Bender

Doctor of Philosophy in Computer Science

University of California, Los Angeles, 2019

Professor Jens Palsberg, Chair

The multi-core revolution has pushed programmers and algorithm designers to build algorithms that leverage concurrency. This notoriously difficult task is futher complicated by the existence of weak architecture and language memory models. The presence of many such memory models has traditionally forced correctness proofs for lock-free concurrent algorithms to be performed on a per-model basis, resulting in a significant duplication of effort. We demonstrate that the correctness of lock-free concurrent algorithms can be proved once for implementations that can be compiled to run correctly and efficiently on all mainstream memory models.

The dissertation of John Bender is approved.

Lei He

Todd Millstein

Miryung Kim

Jens Palsberg, Committee Chair

University of California, Los Angeles 2019

#### TABLE OF CONTENTS

| 1 | Intro | oductio | on                                           | 1  |

|---|-------|---------|----------------------------------------------|----|

|   | 1.1   | Sequer  | ntial Consistency                            | 2  |

|   | 1.2   | Sequer  | ntial Inconsistency                          | 4  |

|   | 1.3   | Specifi | ed Orders                                    | 5  |

|   | 1.4   | In The  | ory and in Practice                          | 6  |

| 2 | Fast  | Code f  | rom Specified Orders                         | 7  |

|   | 2.1   | Fence ? | Insertion                                    | 7  |

|   |       | 2.1.1   | TL2 Commit                                   | 8  |

|   |       | 2.1.2   | Our Approach                                 | 12 |

|   |       | 2.1.3   | Orders, Not Fences                           | 14 |

|   | 2.2   | The Fe  | nce Insertion Algorithm                      | 14 |

|   |       | 2.2.1   | The Core Algorithm                           | 15 |

|   |       | 2.2.2   | Multiple Kinds of Fences                     | 22 |

|   | 2.3   | Implen  | nentation                                    | 23 |

|   | 2.4   | Experi  | mental Results                               | 25 |

|   |       | 2.4.1   | Declaration of Execution Orders              | 26 |

|   |       | 2.4.2   | Parry's Execution Time                       | 28 |

|   |       | 2.4.3   | Experiments with the Four Classic Algorithms | 29 |

|   |       | 2.4.4   | Transactional Memory Algorithms              | 29 |

|   |       | 2.4.5   | Impact of Order Elimination                  | 30 |

|   |       | 2.4.6   | Performance Benchmarks                       | 31 |

|   |       | 2.4.7   | TL2 and TL2 Eager Measurements               | 31 |

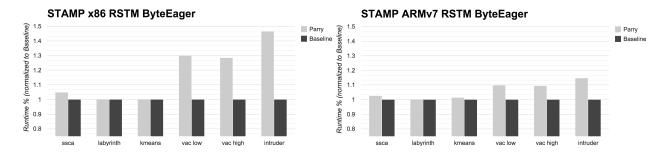

|   |     | 2.4.8                              | RSTM ByteEager Measurements     | 35 |

|---|-----|------------------------------------|---------------------------------|----|

|   | 2.5 | Summa                              | ary                             | 38 |

| 3 | Gen | eral Re                            | asoning with Specified Orders   | 39 |

|   | 3.1 | Relatir                            | ng Memory Models                | 39 |

|   | 3.2 | We're                              | JAMing                          | 41 |

|   | 3.3 | Distinguishing Features of the JAM |                                 |    |

|   |     | 3.3.1                              | Acyclic Causality               | 43 |

|   |     | 3.3.2                              | Letting Go of Release Sequences | 44 |

|   |     | 3.3.3                              | Partial Coherence Order         | 46 |

|   | 3.4 | Axiom                              | atic Model                      | 47 |

|   |     | 3.4.1                              | Plain & Opaque Mode             | 47 |

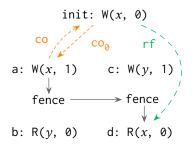

|   |     | 3.4.2                              | Fences                          | 51 |

|   |     | 3.4.3                              | Release-Acquire Mode            | 53 |

|   |     | 3.4.4                              | Volatile Mode                   | 54 |

|   |     | 3.4.5                              | Atomic Read-Writes              | 56 |

|   |     | 3.4.6                              | Summary                         | 58 |

|   | 3.5 | Validat                            | tion                            | 58 |

|   |     | 3.5.1                              | Comparison with ARMv8           | 59 |

|   |     | 3.5.2                              | Comparison with RC11            | 61 |

|   |     | 3.5.3                              | Comparison with x86             | 66 |

|   | 3.6 | Metath                             | neory                           | 67 |

|   |     | 3.6.1                              | Semantics                       | 67 |

|   |     | 3.6.2                              | Theorems                        | 70 |

|   | 37  | Unoba                              | arvable Total Coherence Order   | 73 |

|   | 3.8  | Summary                                                           | <i>'</i>       |

|---|------|-------------------------------------------------------------------|----------------|

| 4 | Prov | ving Correctness with Specified Orders                            | <sup>7</sup> 6 |

|   | 4.1  | Operational Expression Semantics                                  | 77             |

|   | 4.2  | Logic                                                             | 30             |

|   |      | 4.2.1 Assertions and Deductive Rules                              | 31             |

|   |      | 4.2.2 Semantics                                                   | 34             |

|   |      | 4.2.3 Soundness                                                   | 35             |

|   | 4.3  | Proof by Write Elimination: Dekker                                | 35             |

|   |      | 4.3.1 Dekker                                                      | 36             |

|   |      | 4.3.2 Write Elimination with Sequential Consistency and the JOM 8 | 37             |

|   |      | 4.3.3 Expression Equalities                                       | 90             |

|   |      | 4.3.4 Reads to Memory                                             | 91             |

|   |      | 4.3.5 Theorem 7                                                   | 92             |

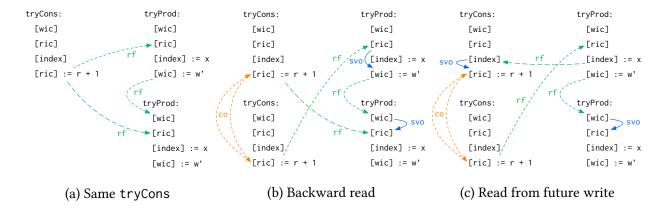

|   | 4.4  | Induction on the Coherence Order: RingBuffer                      | 93             |

|   |      | 4.4.1 RingBuffer Algorithm and Specification                      | 93             |

|   |      | 4.4.2 Individual Invariants                                       | 97             |

|   |      | 4.4.3 Collective Invariants                                       | 98             |

|   |      | 4.4.4 Lemma 5 and Theorems 8 and 9                                | <b>9</b> 9     |

|   | 4.5  | Summary                                                           | )1             |

| 5 | Dala | ated Work                                                         | าว             |

| J | 5.1  | Fence Insertion                                                   |                |

|   | 5.2  | Memory Models                                                     |                |

|   |      | Verification                                                      |                |

|   | L ') | Vontroction                                                       |                |

| 6  | Conclusion                                                              |    |  |  |  |

|----|-------------------------------------------------------------------------|----|--|--|--|

| Re | References                                                              |    |  |  |  |

| A  | Classic Concurrent Algorithms and Specified Orders                      |    |  |  |  |

|    | A.1 Dekker's Mutex                                                      | 17 |  |  |  |

|    | A.2 Parker Mutex                                                        | 17 |  |  |  |

|    | A.3 Peterson's Mutex                                                    | 20 |  |  |  |

|    | A.4 Lamport's Mutex                                                     | 20 |  |  |  |

| В  | Fence Insertion Algorithm Correctness Proof                             | 24 |  |  |  |

| C  | Full Herd Model for the JAM                                             | 27 |  |  |  |

| D  | Specified Orders in the JAM: A Mapping for ARMv8 and x86 Read-writes 12 | 29 |  |  |  |

| E  | Observable Total Coherence for ARMv8                                    | 30 |  |  |  |

| F  | Full Expression Semantics                                               | 33 |  |  |  |

|    | F.1 Expression Rules                                                    | 33 |  |  |  |

|    | F.2 State and Thread Rules                                              | 34 |  |  |  |

|    | F.3 Init Rules                                                          | 34 |  |  |  |

| G  | Full Logic                                                              | 35 |  |  |  |

|    | G.1 Core                                                                | 35 |  |  |  |

|    | G.2 Inequality                                                          | 36 |  |  |  |

|    | G.3 Expressions                                                         | 37 |  |  |  |

|    | G.4 Memory                                                              | 38 |  |  |  |

| Н  | The match Function and actionid Predicate                               | 10 |  |  |  |

| Ι | Soundness Examples             | 143 |

|---|--------------------------------|-----|

| J | Herlihy/Wing Queue Correctness | 145 |

## LIST OF FIGURES

| 1.1  | Message Passing                                      | 3  |

|------|------------------------------------------------------|----|

| 1.2  | MP Graph                                             | 4  |

| 1.3  | MP Extra Access                                      | 5  |

| 2.1  | STAMP TL2 TxCommit Procedure                         | 8  |

| 2.2  | Architecture Definitions                             | 10 |

| 2.3  | Derivation of $W(lock) \rightarrow R(x)$ in TxCommit | 11 |

| 2.4  | Fence Insertion for a Modified Control Flow Graph    | 12 |

| 2.5  | An example graph and its refinement                  | 20 |

| 2.6  | Orders and fences for four classic algorithms        | 27 |

| 2.7  | Algorithm Procedure Size                             | 28 |

| 2.8  | Parry Execution Times, Full Order Elimination        | 32 |

| 2.9  | Parry Execution Times, Linear Elimination            | 32 |

| 2.10 | Orders and fences for TL2 and TL2 Eager              | 33 |

| 2.11 | TL2 Lines to Orders                                  | 33 |

| 2.12 | TL2 Performance Benchmarks                           | 35 |

| 2.13 | Orders and fences for RSTM ByteEager                 | 36 |

| 2.14 | RSTM                                                 | 36 |

| 2.15 | RSTM ByteEager Performance Benchmarks                | 38 |

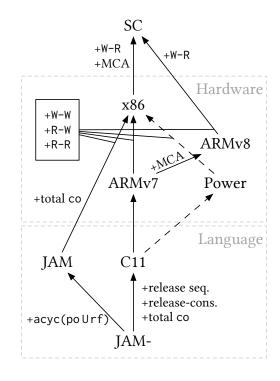

| 3.1  | Memory Models                                        | 40 |

| 3.2  | Causal Cycles                                        | 43 |

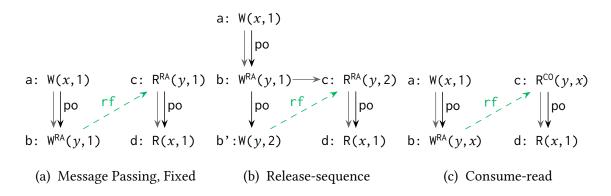

| 3.3  | Release sequences and Consume-reads                  | 45 |

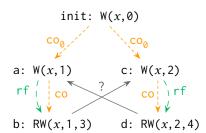

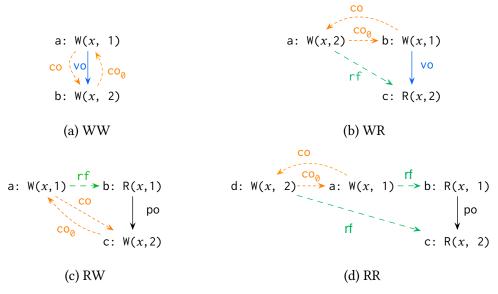

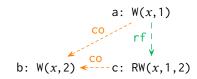

| 3 4  | Concurrent Read-writes                               | 46 |

| 3.5  | Message Passing Coherence                       | 48 |

|------|-------------------------------------------------|----|

| 3.6  | Opaque Mode                                     | 49 |

| 3.7  | Coherence                                       | 51 |

| 3.8  | Specified Visibility                            | 53 |

| 3.9  | Fences, One side                                | 53 |

| 3.10 | Push order, One side                            | 53 |

| 3.11 | Release-Acquire MP                              | 54 |

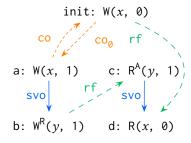

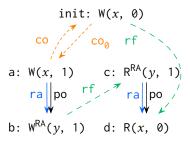

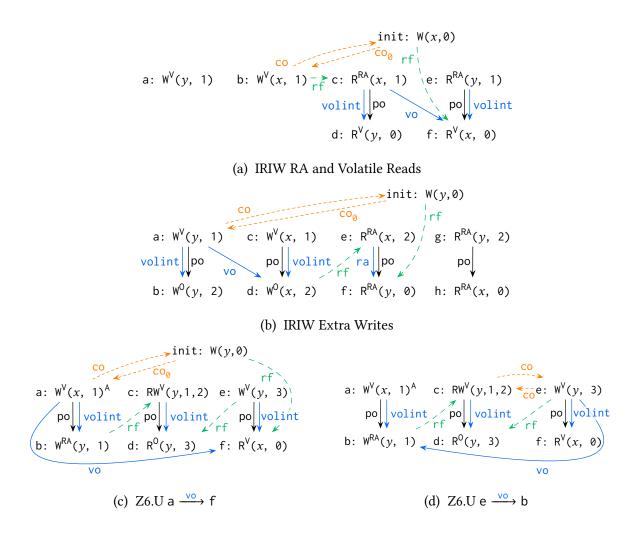

| 3.12 | IRIW Variants                                   | 56 |

| 3.13 | Read-write Exclusivity                          | 57 |

| 3.14 | ARMv8 Litmus Test Comparison                    | 59 |

| 3.15 | ARMv8 Mapping                                   | 60 |

| 3.16 | RC11 & x86 Litmus Test Comparison               | 63 |

| 3.17 | Z6.U & IRIW RA with Volatile Reads Litmus Tests | 64 |

| 3.18 | Syntax                                          | 68 |

| 3.19 | Semantics                                       | 68 |

| 4.1  | Imperative Syntax                               | 78 |

| 4.2  | Semantics                                       | 78 |

| 4.3  | Example Execution                               | 79 |

| 4.4  | Logical Assertion Language and Semantics        | 82 |

| 4.5  | Example Rules                                   | 83 |

| 4.6  | Coherence Order Induction                       | 83 |

| 4.7  | Dekker's Mutex                                  | 86 |

| 4.8  | First Write Elimination, Dekker, SC             | 87 |

| 4.9  | All Write Eliminations, Dekker, SC and RMC      | 88 |

| 4.10 | Equational Reasoning             | 90  |

|------|----------------------------------|-----|

| 4.11 | Write Elimination Proof          | 93  |

| 4.12 | RingBuffer                       | 95  |

| 4.13 | Two-thread Invariant Cycles      | 98  |

| 5.1  | Peterson Victim                  | 106 |

| A.1  | Dekker's Mutex                   | 118 |

| A.2  | Parker                           | 119 |

| A.3  | Peterson's Mutex                 | 120 |

| A.4  | Lamport's Mutex                  | 121 |

| A.5  | Lamport's Mutex, Bad Execution 1 | 122 |

| A.6  | Lamport's Mutex, Bad Execution 2 | 123 |

| F 1  | Two Flagged Executions           | 132 |

# **CHAPTER 1**

#### Introduction

The multi-core revolution has increased the need for shared-memory concurrent programming, algorithms, and languages. In response, programmers target multiple cores to speed up execution, algorithm designers develop concurrent libraries, and language designers make these tasks as easy as possible. Despite much progress, achieving general correctness results remains a challenge, because, in addition to reasoning about the nondeterminism of concurrent programs, a programmer must also reason in the context of a *memory model*.

Intuitively, a memory model is an interface that presents an idealized computer architecture, amenable to reasoning about correctness. A proof of correctness *assumes* a memory model, and then tool support *enforces* that memory model on a real architecture. This separation of concerns, proof from implementation, can simplify the proofs and make them more general, decreasing duplication of effort.

For example, the work of [35] assumes that the memory model is Sequential Consistency and proves the correctness of many algorithms. Then a tool made to support Sequential Consistency can enforce correctness on many architectures by, for example, inserting fences [4]. Similarly, Java algorithms rely on volatile variable annotations that the Java virtual machine enforces using fences [50]. Independently, many algorithms have been proven correct for the C/C++ memory models [81] that are enforced by compilers such as GCC and Clang.

However, this separation of concerns can also negatively impact performance. For example, many of the proofs in Herlihy and Shavit's book remain valid for memory models that are "weaker" than Sequential Consistency. The reason is that each of those proofs relies on a few assumptions, particular to the algorithm, that are implied by Sequential Consistency. The same is true of the relatively weak release-acquire fragment of C++ for certain algorithms [19]. Enforcing

these stronger assumptions is unnecessary and this translates into extra synchronization which hurts performance.

All this leads us to ask: can we get performance, generality, and correctness? Indeed, we will demonstrate that the correctness of lock-free concurrent algorithms can be proved once for implementations that can be compiled to run correctly and efficiently on all mainstream memory models. Specifically, we will describe the tools and techniques we have developed toward that end; including a compiler, the first memory model for Java's Access Modes [52, 51, 41], and a mechanized logic. In the spirit of Java's slogan "write once, run anywhere" and in recognition of our model of Java's Access Modes which forms the basis for our verification efforts, we say that algorithm designers can now "prove once, run efficiently anywhere."

The key to our approach is the use of *specified orders*. The idea is that the correctness of lock-free concurrent algorithms frequently turns on the ordered execution of a few critical instructions regardless of the target architecture or language.

To begin, we will show how one can arrive at the idea of specified orders naturally from an understanding of the relationship between sequential consistency and weaker memory models. First, we will describe sequential consistency informally. Then we will make the definition more precise so that we can accurately describe what is "weakened" in a weak memory model. Then we will see that specified orders arise from a desire to recover some of the ordering guarantees made by sequential consistency while benefiting from the performance of weaker memory models. Throughout we will use simple example programs to illustrate key ideas. Finally, we will conclude with an outline for how we will use specified orders to get fast, general, and correct algorithms in the rest of this work.

## 1.1 Sequential Consistency

Sequential consistency (SC) is the model that most programmers think of when they are reasoning about concurrent programs that access shared memory [48]. Conceptually, under SC, the processor chooses a thread from a set of threads defined by the running program. The processor then executes the next, unexecuted instruction from the chosen thread; here we are primarily

concerned with memory access instructions. The effect of each such memory access is recorded in main memory before choosing the next thread and memory access to execute. Finally, reads can look at main memory for a given location and produce the current value.

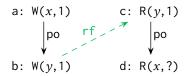

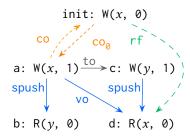

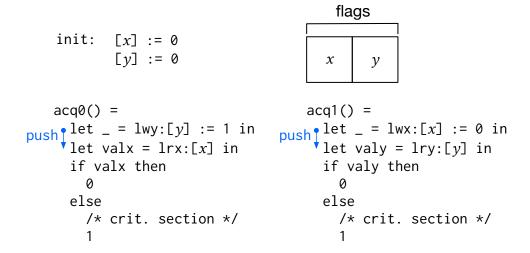

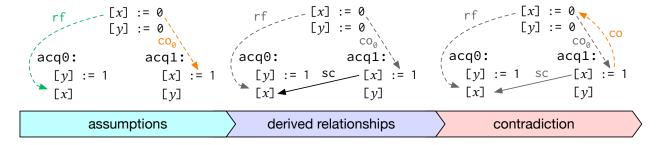

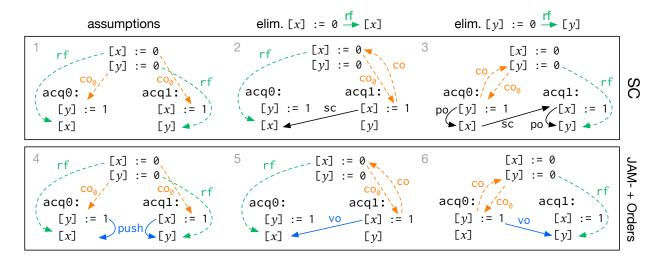

To see how reasoning proceeds under SC, consider the program in Figure 1.1. This program represents a standard message passing idiom in concurrent programming. The program performs two writes, [x] := 1 and [y] := 1, to the locations x and y, concurrently with two reads, [y]

$$[x] := 1$$

$|| r1 := [y]$   $[y] := 1$   $|| r2 := [x]$

Figure 1.1: Message Passing

and [x], of the same locations into the registers r1 and r2. The idea is, when the read of y in the second thread sees the value 1 it's a signal that some work has completed before the write to y in the first thread. In this case the "work" is the write of 1 to x. As an example, this technique is commonly used when constructing locks, where the write to y would be an unlock signaling that the lock of y is available to be acquired. Then, any process that acquires the lock can be assured that the work done in the critical section before the unlock has been written to memory.

We can phrase the desired behavior for this program as a question and use our understanding of sequential consistency to formulate an answer. The question is, if the read of y sees the value 1, then will the read of x see the completed write to x and the value 1? If we know that the read of y saw 1 we know that the write to y was executed. Intuitively, that means the write to x must have been executed since it comes before the write to y. From this we can conclude that the read of x sees the value 1 written by the write to x.

We can make this kind of reasoning more concrete by formalizing SC as three guarantees. These guarantees take the form of relationships between memory accesses in program executions.

- 1. There exists a total order over all executed memory accesses. Intuitively, the total order represents the order in which memory accesses are executed as the processor chooses a thread and an access.

- 2. The total order must be consistent with the order of instructions as defined in the program (program order). This represents the fact that the "next" instruction is determined by the sequence of the accesses in the chosen thread.

3. When a read is paired with a write to the same location (reads-from), the write must be the latest for that location in the total order. This represents the ability of a read to inspect the current state of global memory to find the latest value written to a given location.

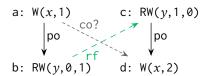

Now we can ask questions about programs and use the formal definitions to provide precise answers. Consider the example execution in Figure 1.2 for the message passing program. Here, we represent an execution as a graph. Memory accesses are labeled nodes with a type of operation, a memory location, and a value. For example, the

Figure 1.2: MP Graph

write to x of the value 1 labeled a appears as a: W(x, 1). The relationships between accesses are labeled edges. Program order is represented as  $\xrightarrow{po}$  and reads-from is represented as  $\xrightarrow{rf}$ . Any accesses not related by program order are assume to be in different threads.

Now the question is, for executions where the message has been passed, b  $\xrightarrow{rf}$  c, will d see the work performed by a? In the graph we can see that a  $\xrightarrow{po}$  b  $\xrightarrow{rf}$  c  $\xrightarrow{po}$  d. Since the total order for execution guaranteed by SC must be consistent with these edges by guarantees 2 and 3, we know that a is executed before d in the total order. Thus, a is the latest write to x and d must see a and read the value 1 by guarantee 3.

## 1.2 Sequential Inconsistency

Much to the consternation of programmers [46] and researchers [62, 58], mainstream processors and languages do not have SC semantics. In the interest of improving performance they provide only a small subset of the relationships guaranteed by SC. For example, ARM processors may execute accesses to different locations out of program order.

To see the effect this has, we return to the message passing example in Figure 1.2. Under a weak memory model, like ARM, the order in which memory accesses are executed is *not* guaranteed to be consistent with program order. In particular we are no longer guaranteed that the edges a  $\xrightarrow{po}$  b and c  $\xrightarrow{po}$  d will affect the order in which the related accesses are executed. So,

even though the message may be received,  $b \xrightarrow{rf} c$ , we can't conclude that d will see the value 1 as written by a. For example, the access a could be executed after b on ARM processors. Similarly, d could be executed before c.

### 1.3 Specified Orders

We can see in the message passing example that there are two ordering relationships guaranteed by SC that are required to ensure the correct behavior, namely the program order relationships a  $\xrightarrow{po}$  b and c  $\xrightarrow{po}$  d. Importantly, these are the *only* relationships that are required and we call these relationships specified orders. Other guarantees made by SC that are unrelated to the correctness of a given algorithm can be sacrificed in the name of performance.

Consider the extension to the message passing example in Figure 1.3. The specified orders now appear in blue along side the program order edges they are intended to recover. Further, there is now another write, e, to different variable z in the first thread. Recall that our only concern in message passing is that memory accesses before the write to y in the program are completed before memory accesses after the read of y in the program, specifically the write to x and the read of x respectively.

Figure 1.3: MP Extra Access

The desired behavior does *not* depend on the write to z executing in any particular order and it can freely be reordered before the other accesses in the first thread. That is, the guarantee that e executes after a and b provided by SC is unnecessary. This allows us to benefit from any performance increase we might see by reordering those accesses and our algorithm will continue behave correctly  $^1$ .

$<sup>^{1}</sup>$ When the message passed is an unlock for the variable this freedom to reorder accesses like the write to z is known as roach motel reordering [77]. The idea is that any access outside a critical region in the program can be reordered to execute inside the critical section without issue.

## 1.4 In Theory and in Practice

Specified orders are an intuitive response to the lack of guarantees provided by modern hardware and compilers. However, we will demonstrate that they can be more than an idealized form of synchronization. Indeed, we will show that they enable us to construct single algorithm that can be compiled to fast, practical code for many architectures.

In Section 2 we demonstrate the practicality of specified orders. We will show that specified orders can be compiled to efficiently synchronized code for the x86 and ARMv7 architectures. In Section 3 we build a formal model for Java's Access Modes [52, 51] and demonstrate that the core of the model admits more weak memory model behaviors than any other mainstream memory model. We will also show why this makes it an ideal target for general reasoning. In Section 4 we build on our formal model of Java's Access Modes and detail a logic we have constructed that we use in mechanized correctness proofs of lock-free algorithms with specified orders. We demonstrate the capabilities of the logic with proofs for a ring buffer as found in the Linux kernel [38] and Dekker's mutual exclusion algorithm. Finally, in Section 5 we place this work in the broader context of research for verification under weak memory models.

## **CHAPTER 2**

# **Fast Code from Specified Orders**

While specified orders are a natural extension to formal relational models of weak memory, they are more than just a theoretical concern. Here, we will demonstrate that specified orders are practical and result in *fast* code. Specifically, we will show that memory fences can be inserted intelligently to enforce specified orders for many processor architectures and the resulting code is competitive with hand written equivalents.

In Section 2.1 we will give an overview of the challenges inherent in inserting fences to enforce specified orders. In Section 2.2 we will detail our algorithm for inserting fences. In Section 2.3 we will provide implementation details for our fence insertion tool, Parry, which implements the algorithm. In Section 2.4 we demonstrate that our approach results in code that is as fast as code written by experts.

#### 2.1 Fence Insertion

To enforce the correct ordering of memory accesses architectures provide memory fence instructions. These instructions guarantee that some subset of the supported memory operations will take place before and after the fence during execution. For example, on ARM processors, the dmb st fence guarantees that all stores before the fence in program order will complete before the fence is finished executing, thereby ordering those stores with instructions after the fence. In the case of the message passing example in Figure 1.2 we can insert a dmb st fence between a and b to ensure that the store to x completes before the store to y.

The problem of enforcing specified orders becomes more complicated when considering portability between architectures. For the message passing example, the specified orders require no

```

#ifndef TL2_EAGER

# ifdef TL2_OPTIM_HASHLOG

for (wr = logs; wr != end; wr++)

# endif

{

// write the deferred stores

WriteBackForward(wr);

}

#endif

// make stores visible before unlock

MEMBARSTST();

// release locks and increment version

DropLocks(Self, wv);

// ensure loads are from global writes

MEMBARSTLD();

return 1;

...

```

Figure 2.1: STAMP TL2 TxCommit Procedure

fences on x86. On ARM processors the specified order in the first thread can be enforced by either a dsb, dmb, or a dmb st. Similarly the specified order in the second thread can be enforced by either a dsb, dmb, or a dmb 1d. These choices have an impact on the performance of the algorithm during execution. We call these choices *fence selection*. Additionally we consider the placement or insertion of fences. For the message passing example the placement is straightforward but this is not always the case.

#### **2.1.1 TL2 Commit**

We will illustrate the complexity of *fence insertion* by examining the commit procedure of the TL2 transactional memory algorithm which we will reference throughout this section.

Intuitively, a transactional memory [34, 79] is a concurrent object that encapsulates and manages accesses to an array of memory locations. The TM interface has four highly concurrent methods, namely init, read, write, and commit, that a typical user program calls a large number of times.

When TL2 is managing a transaction, stores made inside the transaction do not go to main memory. Instead TL2 records the stores in a "write-set". When the transaction ends, the algorithm attempts to acquire locks for each address, commit the write-set to main memory, and release the acquired locks.

For TL2's commit to function properly the "real" stores made to each memory address from the write-set must be seen to take place before the release of the corresponding locks. Otherwise, an external observer may see an address in the write-set as unlocked before the actual store from the write-set makes it to main memory.

Similarly, the release of the lock for each address must be seen to take place before any load after the commit is finished. This ensures that loads performed in the same thread as the transaction will see the same values in memory from the write-set and locks as any external observer.

Figure 2.1 shows the source code for these orders from the TL2 commit procedure, TxCommit, as it appears in implementation included with the STAMP benchmark suite [24]. The WriteBackForward procedure contains the store instruction that moves values from the write-set to main memory and the DropLocks procedure contains the store instruction that releases the locks.

We record the specified orders from WriteBackForward(wr) to DropLocks(Self, wv) and from DropLocks(Self, wv) to all later loads (...) as blue arrows. To enforce these orders, the TL2 designers have placed memory fence macros between the relevant operations. An implementer who is porting TL2 to different architectures can define each macro to be an architecture appropriate memory fence to enforce the correct behavior. The drawback of such a fence-centric approach is that for a programmer who wishes to understand the TM algorithm and perhaps to port it to a different architecture, a fence placement says little about why the designers chose it and placed it at a particular program point. Fences are best viewed as an implementation mechanism for a higher level of abstraction.

**Fence Insertion.** Inserting fences requires knowledge of the control flow paths between the ordered instructions, as well as the other instructions on those paths.

Without knowing the control flow information it is possible to miss paths and allow executions in which the instructions may be seen to pass each other. On the other hand, a naive

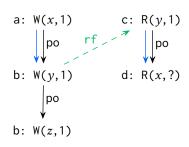

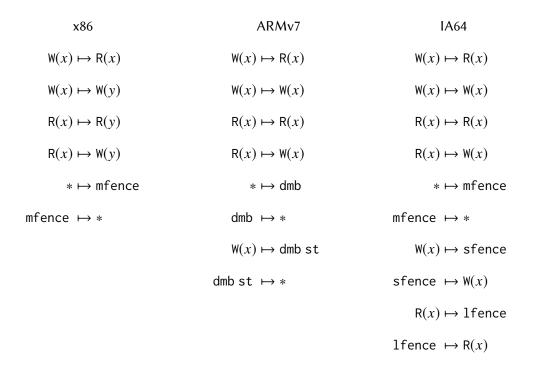

Figure 2.2: Architecture Definitions

approach to fence placement that avoids missing paths by inserting a fence directly after the first instruction in the order can be expensive. For example, if the first fence macro is placed directly after the call to WriteBackForward it can result in an expensive loop over the fence when the TL2\_OPTIM\_HASHLOG flag is set at compile-time.

Without knowing the other instructions in the control flow paths, one might place a new fence where another already exists, or where properties of the memory models makes fences unnecessary in the presence of other instructions.

For example, consider the first order in TxCommit. The x86 memory model already enforces many orders. Looking at the orders enforced by the x86 architecture definition in Figure 2.2, we can see  $W(x) \mapsto W(y)$  suggests that two stores to any address will not move past each other. We use this to prove that the instructions in the first order of TxCommit,  $W(addr) \to W(lock)$ , will not move past each other:

$$p, x86 \vdash W(addr) \rightarrow W(lock)$$

$$\underbrace{\frac{p, \mathsf{x86} \vdash \mathsf{W}(\mathsf{tmp}) \to \mathsf{R}(\mathsf{tmp}) \quad p, \mathsf{x86} \vdash \mathsf{R}(\mathsf{tmp}) \to \mathsf{R}(x)}_{p, \, \mathsf{x86} \vdash \mathsf{W}(\mathsf{lock}) \to \mathsf{R}(x)}}_{p, \, \mathsf{x86} \vdash \mathsf{W}(\mathsf{lock}) \to \mathsf{R}(x)}$$

Figure 2.3: Derivation of  $W(lock) \rightarrow R(x)$  in TxCommit

That is, if x86 prevents stores from moving past each other and the order we want to enforce involves two stores, then we can conclude that the order is enforced. This means we can safely define the first macro in the example as a no-op on x86. Note that our architecture rules for x86 do not include non-temporal hinted store instructions like movnti and movntdq.

In contrast, this order is not enforced by ARMv7. Since stores can be seen to move past other stores when the addresses are different on ARMv7 we do not include this rule in the architecture definition. Instead the rule relating stores requires that the addresses be the same.

The second order in TxCommit,  $W(lock) \rightarrow R(x)$ , represents a more complex example of how intervening instructions can affect order enforcement. When TxCommit is compiled with Clang, the compiler generates a store and a load to the same temporary address after the lock release in DropLocks but before the end of the procedure as illustrated in both graphs in Figure 2.4. We can use these instructions and the properties of x86 to prove the *transitive order* in Figure 2.3 where tmp represents the temporary memory location. We conclude that the store to lock can never be seen to move past the final load in TxCommit and also any subsequent load. We define the notation, rules and memory model properties more completely in the next section.

**Selecting Fences.** Selecting the correct fence requires knowledge of how the compiler will treat the source code and knowledge of the fences available for each architecture. For TxCommit on ARMv7 the second macro can be defined correctly using many different fence configurations according to the ARM documentation [6], e.g. dsb, dmb, or a qualified dmb st. Both the litmus test documentation [32] and the assembler reference [6] are complicated texts in accordance with the complexity of the ARMv7 memory model. Determining the best fence is a nontrivial task.

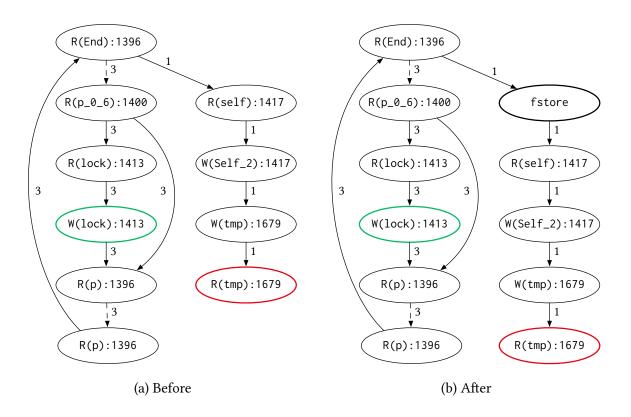

Figure 2.4: Fence Insertion for a Modified Control Flow Graph

#### 2.1.2 Our Approach

We decompose fence insertion into two sub-problems. First we eliminate any orders that are provably enforced by existing instructions and the properties of the target architecture. For the remaining orders we modify the program with new instructions that enforce the remaining orders.

We address both sub-problems by considering control flow graphs with a restricted set of instructions. Each node is labeled with the instruction, the address that it operates on, and the line number that it was generated from in the source code. Every path between two instructions in the control flow graph represents a possible execution involving those instructions. We construct these graphs using the intermediate representation and control flow graph for a given procedures as generated by the LLVM compiler [49].

In Figure 2.4a we have a control flow sub-graph for the second order in TxCommit, constructed from LLVM's output when compiling the procedure. It contains all of the paths and a subset of

the instructions (elided with dashed arrows) that appear between the store, W(lock), to release the locks in DropLocks and the end of the TxCommit procedure. Note that the store to release the locks appears in a cycle that comes from the body of the DropLocks procedure though it does not appear in the code in Figure 2.1. Also the name of the variable containing the lock address has been renamed to lock for clarity.

**Order Elimination.** We eliminate an order by proving that the order is enforced for every path between the ordered instructions. Proofs for orders correspond with paths in the graph through a second set of *architecture edges*. If two instructions exist in a control flow path and the architecture guarantees that they will never move past each other, we add an architecture edge.

Returning to our example, recall that on x86 we can eliminate the second order in TxCommit because the compiler generates a load and store to a temporary variable. In Figure 2.4a, we add architecture edges (not pictured) between two nodes pairs. We add the first edge between the nodes labeled with W(lock):1413 and W(tmp):1679 because stores cannot move past stores. We add the second edge between the nodes labeled with W(tmp):1679 and R(tmp):1679 because stores can not move past loads from the same address. These edges correspond with a transitive order derivation for every path between the store to lock and the load to tmp. As a result we can eliminate the order.

In contrast, on ARMv7, we cannot add the first architecture edge between the store to lock and the store to tmp because stores are permitted to move past other stores for different addresses. In that case, since we can't eliminate the order with the original graph, we must alter the graph so that we can prove the order is enforced.

Fence Insertion. We model the problem of finding these graph alterations as minimum multi-commodity cut [18] (hereafter multi-cut). Intuitively, multi-cut finds a minimum set of edges such that, when they are removed, no paths exist between the sources and sinks for all commodities. If we define the sources and sinks for commodities using the paired instructions in orders and then "split" the edges in the resulting cut with a fence, we will have transitive orders for all paths and all orders.

The altered control flow graph in Figure 2.4b shows the results of fence insertion on ARMv7

for TxCommit. The algorithm selects a single edge from the original graph to split with a fence, represented here as fstore. This alteration ensures that all paths from the store to the load are provably enforced.

Note also that the cut should happen outside the loop-cycle in the control flow graph. This prevents an unnecessary performance penalty when placing the fence. This is handled directly by the minimum cut algorithm. Since the cut is determined based on the sum of the capacities of the edges in the cut, we can use larger capacities to discourage the selection of edges that occur in loops. This ensures a fence will only be placed in a loop when all paths for an order are in a loop. Modeling fence insertion as multi-cut accounts for the full generality of control flow graphs including odd control flow configurations and order overlap.

**Fence Selection.** Finally, we select appropriate fences for each placement by defining a partial order over fences based on their capabilities. For example on ARMv7 a dmb fence can enforce strictly more orders than dmb st since the latter only waits for stores. In the case of Figure 2.4 either fence will work but we prefer the "weaker" dmb st represented here as the abstract fence type fstore. We do this under the assumption that it is less costly during execution which is supported by the ARMv7 documentation [32].

#### 2.1.3 Orders, Not Fences

The memory fence is a blunt instrument that relates possibly hundreds of instructions across many execution paths and blurs its original purpose. Instead we supply a scalpel in the form of specified orders, which are more specific about the desired behavior of the program. Specified orders at the source level enable authors to reason more easily about their algorithm, while a compiler can do the work to insert fences that enforce the orders.

## 2.2 The Fence Insertion Algorithm

Our algorithm for fence insertion takes three inputs: a control-flow graph G, architecture rules A, and specified orders O. The output is a transformed graph Insert(G, A, O) with fences that

enforce the specified orders. In Section 2.2.1, we define a basic version of Insert and prove it correct. The basic version relies on the simplifying assumption that the only fence available is fany. We will assume that fany enforces that all instructions prior to the fence happen before all instructions after the fence. In Section 2.2.2, we describe briefly how to generalize Insert to work with multiple fences.

#### 2.2.1 The Core Algorithm

We proceed as follows. First we define the basic concepts of graphs, architecture rules, and specified orders, along with some helper notation. Then we define a correctness criterion of the form  $G, A \models O$ , which says that the combination of G and A enforces all the specified orders O. This brings us to definition of our algorithm. Insert whose goal is to produce an output graph G that satisfies  $G, A \models O$ . Finally, we give an example and then prove the correctness of Insert.

**Graphs.** A control-flow graph  $G = (V, E, \ell)$  consists of a set V of nodes, a set  $E \subseteq (V \times V)$  of directed edges, and a labeling function  $\ell$ . Intuitively, a node is a program point, the label of a node is the instruction at that program point, and an edge is potential control flow between two program points. We use i, j to range over V. The function  $\ell$  maps each element of V to a *label*, which is an element of

$$\{ W(a), R(a), fany \}$$

where *a* is an address, W represents a *store*, R represents a *load*, and fany is a fence. We use *l* to range over labels. Notice that our control-flow graphs focus entirely on loads, stores, and fences. This is in contrast to the conventional notion of a control-flow graph that represents every instruction in a program. One can abstract such a conventional graph into one of our graphs by, intuitively, omitting the nodes of no interest to our approach.

For a graph G with  $i_1$ ,  $i_2$  among its nodes, we use paths $(G, i_1, i_2)$  to denote the set of *paths* in G from  $i_1$  to  $i_2$ . A path from  $i_1$  to  $i_2$  is itself a graph in which 1) each node has one outgoing edge, except  $i_2$  which has no outgoing edges, and 2) all nodes on the path are reachable from  $i_1$  by following zero, one, or more edges. Our notion of path is usually known as a *simple path* because it allows no loops. Still, we will use the terminology "path" for simplicity. We will use p to range

over paths.

**Architecture rules.** A set of architecture rules specifies a memory model. Intuitively, the fewer the rules, the weaker the memory model. The idea is that even if a control-flow graph has an edge from  $i_1$  to  $i_2$ , the execution of  $i_1$  and  $i_2$  may happen in either order or overlap, unless specific architecture rules enforce an order of execution. A set A of architecture rules consists of rules of the form  $L \mapsto R$ , where L, R are rule components that range over

$$\{ *, W(x), R(x), fany \}$$

and where x is a variable that ranges over addresses. Intuitively, \* is a wildcard. A rule  $L \mapsto R$  expresses that if we have a graph  $(V, E, \ell)$  with two nodes  $i_1$  and  $i_2$  such that  $i_1$  can reach  $i_2$ , and such that we can *instantiate*  $L \mapsto R$  to  $(\ell(i_1), \ell(i_2))$ , then we can conclude that  $i_1$  must happen before  $i_2$ . We will define the notion of instantiation below.

For example, the rules (\*  $\mapsto$  fany), (fany  $\mapsto$  \*) express, intuitively, that fany is a fence. Specifically, the first rule says that all instructions that can reach the fence will happen before the fence, while the second rule says all instructions that can be reached from the fence will happen after the fence. The combined effect of those two rules is that all instructions prior to the fence happen before all instructions after the fence. In this section we define Insert in a way that relies on that A contains those two rules.

As another example, the rule  $W(x) \mapsto W(y)$  expresses, intuitively, that all store instructions must happen in the order in which they are reached in the control-flow graph.

As a third example, the rule  $W(x) \mapsto R(x)$  expresses, intuitively, that if a store instruction to a particular address can reach a load instruction from that same address in the control-flow graph, then the store instruction must happen before the load instruction.

We will now define a notion of *instantiating* an architecture rule to a pair of labels. Specifically, if  $(L \mapsto R)$  is an architecture rule and  $(l_1, l_2)$  is a pair of labels, then we write  $(L \mapsto R) \triangleright (l_1, l_2)$  to denote that  $(L \mapsto R)$  instantiates to  $(l_1, l_2)$ .

The definition of instatiation will ensure that for rules such as  $(W(x) \mapsto R(x))$ , the two occurrences of x must be replaced with the *same* address. Our technical device to make that happen is that of a *substitution*. We use  $\sigma$  to range over substitutions that map variables of the form

x to addresses. For our use, each substitution has either a domain of either zero, one, or two elements, depending on whether a rule mentions zero, one or two variables. The definition of  $(L \mapsto R) \triangleright (l_1, l_2)$  uses the relation  $\blacktriangleright$  to distribute the use of a substitution to each of L and R. Now we are ready to present the detailed definition of instantiation.

We say that a rule  $(L \mapsto R)$  instantiates to a pair of labels  $(l_1, l_2)$  if we can derive  $(L \mapsto R) \triangleright (l_1, l_2)$  with the following rules:

$$\frac{(L,\sigma) \blacktriangleright l_1 \qquad (R,\sigma) \blacktriangleright l_2}{(L \mapsto R) \trianglerighteq (l_1,l_2)}$$

$$(*,\sigma) \blacktriangleright l$$

$$(\mathbb{W}(x),\sigma) \blacktriangleright \mathbb{W}(\sigma(x))$$

$$(\mathbb{R}(x),\sigma) \blacktriangleright \mathbb{R}(\sigma(x))$$

$$(fany,\sigma) \blacktriangleright fany$$

The first rule says that we can instantiate  $(L \mapsto R)$  to  $(l_1, l_2)$  if we can find a substitution  $\sigma$  such that L guided by  $\sigma$  instantiates to  $l_1$  (written  $((L, \sigma) \triangleright l_1)$ ), and R guided by  $\sigma$  instantiates to  $l_2$  (written  $((R, \sigma) \triangleright l_2)$ ). The other four rules define the cases where a rule component, guided by a substitution, instantiates to a label. Specifically, \* instantiates to any label, W(x) instantiates to  $W(\sigma(x))$ , W(x) instantiates to  $W(\sigma(x))$ , and fany instantiates to fany.

**Specified Orders.** For a graph  $G = (V, E, \ell)$ , the specified orders is a set  $O \subseteq (V \times V)$ .

**Correctness criterion.** We will now define a correctness criterion  $G, A \models O$ . Intuitively,  $G, A \models O$  says that the combination of G and A enforces all the specified orders O. The goal of our approach is to produce an output graph G that satisfies  $G, A \models O$ .

We define the correctness criterion in two steps. First we define a judgment  $p, A \vdash i_1 \rightarrow i_2$ . For a path  $p = (V, E, \ell)$ , architecture rules A, and nodes  $i_1, i_2$  on p, we define that  $p, A \vdash i_1 \rightarrow i_2$  holds if it can be derived by these rules:

$$p, A \vdash i_1 \rightarrow i_2$$

(where  $i_1$  can reach  $i_2$  in  $p \land$

$$(L \mapsto R) \in A \land$$

$$(L \mapsto R) \rhd (\ell(i_1), \ell(i_2)) )$$

$$\underbrace{p, A \vdash i_1 \rightarrow j}_{p, A \vdash i_1 \rightarrow i_2} \underbrace{p, A \vdash i_1 \rightarrow i_2}_{p, A \vdash i_1 \rightarrow i_2}$$

The first rule instantiates an architecture rule in *A*, and the second rule is transitivity.

Now we are ready to define the overall correctness criterion. For a graph  $G = (V, E, \ell)$ , architecture rules A, and specified orders  $O \subseteq (V \times V)$ , define:

$$G, A \models O \iff$$

$$\forall (i_1, i_2) \in O : \forall p \in \mathsf{paths}(G, i_1, i_2) : p, A \vdash i_1 \to i_2$$

Notice that the definition considers *all* paths between  $i_1$  and  $i_2$ . This ensures that the specified order will be enforced, irrespective of the control flow.

**Algorithm overview.** Our algorithm Insert composes three functions Elim, Cut, and Refine. Intuitively, Insert proceeds in three steps:

- 1. Elim determines a subset of the specified orders that are enforced by the architecture.

- 2. Cut determines *where* to insert fences that will enforce the rest of the specified orders.

- 3. Refine inserts the fences.

We now describe Elim, Cut, Refine, and Insert. After those descriptions, we will give an example.

**The Elim function.** Our approach uses a function Elim that determines a subset of the specified orders for which we need *no* fences. We rely on the fact that Elim satisfies the following property:

$$\mathsf{Elim}(G, A, O) \subseteq O \text{ and } G, A \models \mathsf{Elim}(G, A, O).$$

(2.1)

Programmers can implement  $\mathsf{Elim}(G,A,O)$  in many ways, including the trivial approach that always returns the empty set. Our implementation, as a default, uses a straightforward exponential-time algorithm that for each  $(i_1,i_2) \in O$  enumerates all  $p \in \mathsf{paths}(G,i_1,i_2)$ , and for each such p uses brute-force to determine whether  $p,A \vdash i_1 \to i_2$ . The result is that  $\mathsf{Elim}(G,A,O)$  returns a maximal subset of O. The maximal size helps us insert few fences.

In addition we have implemented a linear time approximation algorithm which works by finding enough nodes i with the property,  $\{(i_1,i),(i,i_2)\}$ ,  $A \vdash i_1 \rightarrow i_2$  such that, when every i is removed paths $(G,i_1,i_2)=\emptyset$ .

In either case, we need no modifications to G to enforce the orders in  $\mathsf{Elim}(G,A,O)$  so now let us focus on where to insert fences to enforce the orders in  $O \setminus \mathsf{Elim}(G,A,O)$ .

**The Cut function.** Our approach uses a function Cut that determines *where* to insert fences. We rely on that Cut satisfies the following property:

$$Cut(G, O)$$

is a multi-cut for  $G, O$ . (2.2)

The multi-cut specifies where to insert fences. Let us recall the standard notion of a multi-cut [18]: given a graph  $G = (V, E, \ell)$  and a set  $O \subseteq (V \times V)$ , a multi-cut for G, O is a set K, where  $K \subseteq E$ , such that  $\forall i_1, i_2 \in O$ : paths $((V, E \setminus K, \ell), i_1, i_2) = \emptyset$ . Programmers can implement Cut(G, O) in many ways, such as the trivial approach that always returns E, an approximation algorithm [14], and an integer linear program [14]. We experimented with those and chose an ILP with a polynomial number of constraints in the size of the graph [14]. We use SAGE [73] and the default solver GLPK [30] to solve the ILP, which returns a multi-cut of minimal size, which in turn helps us insert few fences. Given G, O and an integer n, the problem to decide whether there exists a multi-cut for G, O with at most n elements is NP-complete for |O| > 2 [18]. Now let us consider how to use a multi-cut to insert fences.

The Refine function. Our approach uses a function Refine that inserts fences. We will give the definition of Refine in detail and later we will prove that the definition satisfies four lemmas. For a graph  $G = (V, E, \ell)$  and a cut-set K, where  $K \subseteq E$ , the function Refine(G, K) creates a set  $W_K$  of additional nodes (fences!), and replaces each  $(j_1, j_2) \in K$  with two new edges

Figure 2.5: An example graph and its refinement.

that, intuitively, insert a fence between  $j_1$  and  $j_2$ . The new nodes form a set  $W_K$ :

$$W_K ::= \{v_{j_1,j_2} \mid (j_1,j_2) \in K\}$$

where each  $v_{j_1,j_2}$  is a fresh node. The output graph is:

$$\begin{aligned} \text{Refine}(G,K) &= (V \cup W_K, \ (E \setminus K) \cup E_K, \ \ell_K) \\ E_K &= \{(j_1,v_{j_1,j_2}), (v_{j_1,j_2},j_2) \mid v_{j_1,j_2} \in W_K\} \\ \ell_K &= \ell \cup \{(v_{j_1,j_2}, \mathsf{fany}) \mid (j_1,j_2) \in K\} \end{aligned}$$

Notice that  $Refine(G, \emptyset) = G$ .

**The Insert function.** We can now define Insert:

$$Insert(G, A, O) = Refine(G, Cut(G, O \setminus Elim(G, A, O)))$$

The definition calls three functions as outlined above: first Elim, then Cut, and finally Refine. Both Elim and Cut run in worst-case exponential time, while set difference and Refine run in polynomial time, so we conclude that Insert runs in worst-case exponential time.

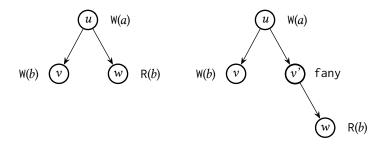

**Example.** Consider the graph  $G = (V, E, \ell)$ , which is illustrated in Figure 2.5 (left graph). We have

$$V = \{u, v, w\} \qquad \ell(u) = W(a)$$

$$E = \{(u, v), (u, w)\} \qquad \ell(v) = W(b)$$

$$\ell(w) = R(b)$$

where *a*, *b* are distinct addresses. Consider also the set of architecture rules:

$$A = \{(* \mapsto \mathsf{fany}), (\mathsf{fany} \mapsto *),$$

$$(\mathsf{W}(x) \mapsto \mathsf{W}(y)), (\mathsf{W}(x) \mapsto \mathsf{R}(x))\}$$

Consider finally the specified orders

$$O = \{(u, v), (u, w)\}$$

A run of Insert(G, A, O) will proceed as follows.

The first step is to call  $\mathsf{Elim}(G,A,O)$ . This call to  $\mathsf{Elim}$  will find that  $G,A \models \{(u,v)\}$  because we have a single-edge path from u to v, and a rule  $(\mathsf{W}(x) \mapsto \mathsf{W}(y)) \in A$  that instantiates to  $(\ell(u),\ell(v))$ , which is equal to  $(\mathsf{W}(a),\mathsf{W}(b))$ . Thus, if p is the single-edge path from u to v, we can derive  $p,A \vdash u \to v$ . The call to  $\mathsf{Elim}$  will also find that  $G,A \not\models \{(u,w)\}$  because we have no rule in A that for the single-edge path p' from u to w enables us to derive  $p',A \vdash u \to w$ . Note here that the rule  $(\mathsf{W}(x) \mapsto \mathsf{R}(x)) \in A$  requires the two instructions (store and load) work with the same address, while the two labels  $\mathsf{W}(a)$  and  $\mathsf{W}(b)$  operate on distinct addresses. In summary, we have  $\mathsf{Elim}(G,A,O)=\{(u,v)\}$ . We can calculate  $O\setminus\{(u,v)\}=\{(u,w)\}$ .

The second step is to call  $Cut(G, O \setminus Elim(G, A, O) = Cut(G, O \setminus \{(u, v)\}) = Cut(G, \{(u, w)\})$ . In this case we have  $Cut(G, \{(u, w)\}) = \{(u, w)\}$ . The reason is that the one path from u to w has a single edge so we must have that edge in the multi-cut.

The third step is to call

$$Insert(G, A, O) = Refine(G, Cut(G, O \setminus Elim(G, A, O)))$$

$$= Refine(G, \{(u, w)\})$$

The result is illustrated in Figure 2.5 (right graph). Compared to G, the graph Insert(G, A, O) has an additional node v', no edge  $\{(u, w)\}$ , but instead two edges (u, v') and (v', w). We have  $\ell(v') = \text{fany}$ , that is, the new node is a fence. We can instantiate the rule  $(* \mapsto \text{fany}) \in A$  to (W(a), fany), and we can instantiate the rule  $(\text{fany} \mapsto *) \in A$  to (fany, R(b)). So for the path p'' with the two edges (u, v') and (v', w), we have that we can derive p'',  $A \models (u, w)$ .

In summary, the example has two specified orders, and one of them is enforced by the architecture without insertion of any fences, while for the other, we inserted a single fence.

**Theorem 1.** If

$$\{(* \mapsto fany), (fany \mapsto *)\} \subseteq A$$

, then  $Insert(G, A, O), A \models O$ .

We prove Theorem 1 in Appendix B.

#### 2.2.2 Multiple Kinds of Fences

Let us now relax the assumption that the only fence available is fany. For example, Figure 2.2 gives rules for the two fences on ARMv7, namely the weaker fence dmb st and the stronger fence dmb. When multiple fences are available, the Refine function can choose as weak a fence as possible. The idea is that a weaker fence executes faster than a stronger fence, which is true for the architectures we have considered. Intuitively, we let Refine choose the weakest fence that enforces the relevant declared executions orders.

We will explain how to make the choice in two steps. First let us consider a simple case, which happens to be the one we encountered exclusively in our experiments. For an edge  $(j_1, j_2)$  in a cut set K, suppose we have a single element  $(i_1, i_2) \in O \setminus \text{Elim}(G, A, O)$  for which  $(j_1, j_2)$  is on a path from  $i_1$  to  $i_2$ . We must chose a fence that is strong enough to enforce the order  $(i_1, i_2)$ . Specifically, we need a fence f such that f contains the rules f and f and f and f such that

$$(L \mapsto f) \triangleright (i_1, f) \land (f \mapsto R) \triangleright (f, i_2)$$

We will choose as weak a fence as possible. For the architectures we have considered, we can always find a fence that is the weakest among all those that satisfy the above requirement.

Now let us consider the general case. For an edge  $(j_1, j_2)$  in a cut set K, suppose we have multiple elements  $(i_1, i_2) \in O \setminus \text{Elim}(G, A, O)$  for which  $(j_1, j_2)$  is on a path from  $i_1$  to  $i_2$ . Here we want the least expensive fence that will enforce all of the involved orders. For each such  $(i_1, i_2)$  we chose a fence  $f_{(i_1,i_2)}$  as described above. Now we need a fence that is at least as strong as those fences  $f_{(i_1,i_2)}$ . Again, for the architectures we have considered, we can always find a weakest fence that is at least as strong as each  $f_{(i_1,i_2)}$ .

**Optimality.** The optimality of our approach to fence selection depends on the assumption that any two fences will always execute more slowly than any single fence. Consider the case of an architecture like IA64 in Figure 2.2 and some procedure where we have a load-load order and a store-store order overlapping on a single simple path. Individually the orders can be enforced with an 1fence *and* an sfence but the optimal multi-cut will include an edge shared by both orders. Then to satisfy both orders with a single fence we must select an mfence.

#### 2.3 Implementation

We have implemented our approach in a tool called Parry [11] that takes as input a concurrent algorithm written in C/C++, declared execution orders, and a memory model, and as output produces C/C++ with fences. Parry uses Python to orchestrate the three major tasks in fence insertion: control-flow graph generation, order elimination, and fence insertion. We will now explain some details of Parry, particularly a few points that go beyond the fence insertion algorithm that we described in Section 2.2.

**Graph Generation** Parry is based on LLVM. First Parry compiles the input source code to LLVM's static-single-assignment (SSA) intermediate representation (IR) along with debugging information. Then Parry generates a control-flow graph of the target procedure using LLVM's opt tool. Next, Parry simplifies the control-flow graph by replacing each standard block with a path of instructions. We manipulate the resulting graphs with the graph-tool library [23].

We construct a graph in which the only nodes are for load, store, call, and cmpxchg instructions. Note that compared to the algorithm in Section 2.2, we add call instructions to safely account for methods which do not get inlined, and we add the cmpxchg instructions because they are frequently used by authors to enforce orders. Indeed, the cmpxchg instruction provides compare-and-swap semantics at the LLVM IR level and can act as a full memory fence (like mfence on x86 or dmb on ARMv7) [72].

**Compiler Assumptions** Parry uses Clang to translate C/C++ into LLVM's intermediate representation and we assume that this translation preserves some key aspects of the code that are of interest to Parry.

We assume that the semantics of a line of C/C++ used to specify an order will be preserved in the intermediate representation generated by Clang. For example, if the programmer expects a store to a certain memory address at a line in the code then we assume that Clang will generate a store to that address for that line. We safely account for the possibility of more than one instruction per line matching the event types of an order by including all matching instructions

during the analysis.

We also assume that our fence placements will remain valid after a compiler optimizes the C/C++ code that Parry outputs. That is, we require that the ordered instructions will not be moved past the fences by the compiler. To that end we ensure that all inline assembly instructions inserted by Parry are marked as volatile operations.

**Architecture Rules** As detailed in Section 2.2 we have created a set of rules for each architecture that describe the which instructions won't "move" during execution. These rules are necessary for order elimination.

We have included three architectures in Figure 2.2, x86, ARMv7 and IA64. The last is for clarity and comparison since our evaluation does not include benchmarks for IA64.

We compiled these rules based on our interpretation of the processor documentation available for each architecture. They are intended to be an over-approximation of the actual architecture behavior. During order elimination they are used to establish preexisting orders without consideration for other types of instructions aside from stores, loads, and fences.

Not included in Figure 2.2 are instructions that exist in the LLVM IR, like cmpxchg, which result in hardware instructions with fence-like semantics. We do account for LLVM's cmpxchg as detailed in Section 2.4.7.

**Edge Elimination** Parry has an initial step that takes place before the main algorithm in Section 2.2: edge elimination. The idea is to eliminate all edges that are irrelevant to the fence insertion problem. We keep an edge only if for at least one declared execution order, the edge is on a path from the source to the sink of the order *and* the instructions on that path don't enforce the order. After edge elimination, we can implement order elimination for an order  $(i_1, i_2)$  simply by checking whether the set of paths from  $i_1$  to  $i_2$  is empty.

**Address Equality** In some cases, an architecture rule uses a variable twice, such as the rule  $(W(x) \to R(x))$ . Our tool only instantiates the rule in case x can be replaced with a variable in LLVM's internal static-single-assignment form. The SSA form guarantees that the value of that

variable is the same at both program points. For example, in Figure 2.4, tmp is a variable, so we can instantiate  $(W(x) \rightarrow R(x))$  to (W(tmp), R(tmp)).

**Fence Insertion** Since our analysis is static and we want to minimize the execution of fence instructions, we avoid placing fences in loops unless absolutely necessary. Parry achieves this by finding cycles in the control flow graph. Then it assigns an edge weight to the cycle edges that is one more than twice the incoming edge weight as illustrated earlier in Figure 2.4. This ensures that even if many orders from outside the loop overlap inside the loop the linear program will prefer edges outside the loop. This heuristic has value if a loop is executed more than once.

Alternate Fence Placements In many cases there are multiple fence placements that are equivalent according to the multi-cut model. That is, there may be edges with weights on similar paths resulting in the same objective function value from the multi-cut linear program. Our implementation selects the edge closest to the source. Our tool is also able to select alternate cuts where necessary and we discuss our experimental evaluation of equivalent alternative fence placements in Section 2.4.7.

# 2.4 Experimental Results

We have evaluated Parry with four classic concurrent algorithms (Dekker, Lamport, Parker, and Peterson) and three transactional memory algorithms (TL2 [24], TL2 Eager, and TLRW [25]). We downloaded implementations of the classic algorithms from the Musketeer project [4]), TL2 and TL2 Eager are from the STAMP project [64], and TLRW from the Rochester Software Transactional Memory library [61]. TL2 Eager is a variant of TL2. The TLRW implementation is named ByteEager. The three TM algorithms have procedures that are significantly more complex than those of the classic algorithms. For example, TL2 has nearly 400 nodes and more than 250 lines of code in one procedure.

We evaluate all of the algorithms on the x86 and ARMv7 architectures. We chose to work with ARMv7 due to its increasing relevance in all types of computing and its particularly weak

memory model, compared to x86.

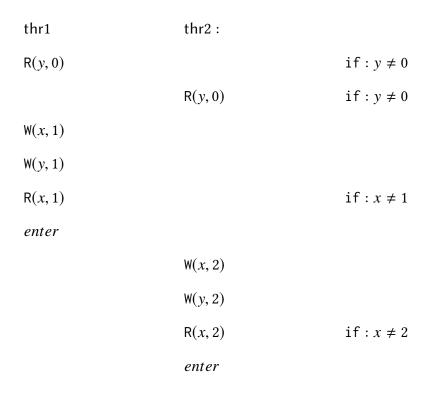

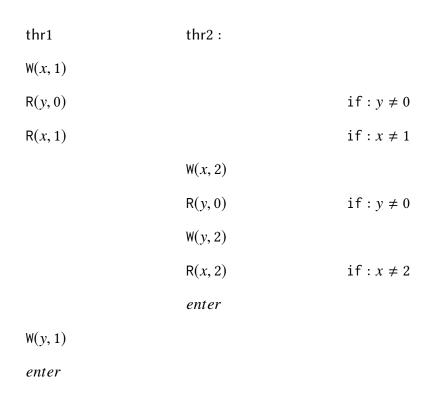

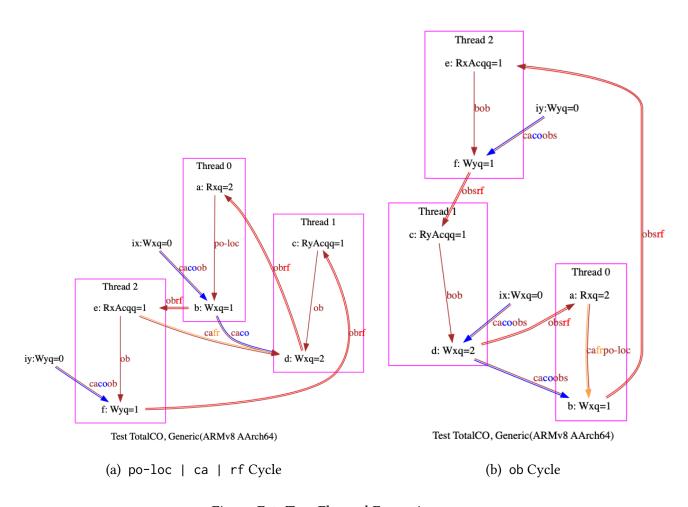

### 2.4.1 Declaration of Execution Orders

We declared execution orders for each of the seven algorithms to benchmark our approach against the author supplied memory fences. We also removed existing fences from the algorithms.

Classic Algorithms Figure 2.6 shows the orders for the four classic algorithms. We got the orders for Dekker from Lesani's dissertation [54] and the orders for Peterson are similar. We got the single order for Parker from a blog post by Dave Dice. Dice wrote that the Parker implementation in the Java Virtual Machine was found to have a bug due to store buffering [26]. We defined an order according to the description of the bug to ensure that the store to the shared variable \_counter is flushed. We defined the orders for Lamport based on an analysis that we detail in an appendix (TODO which appendix).

**TL2 and TL2 Eager** Figure 2.10 shows the orders for TL2 and TL2 Eager which we got from Lesani's dissertation [54]. The source code for both algorithms can be found at [22].

**RSTM ByteEager** Figure 2.13 shows the orders for ByteEager. The source code for RSTM ByteEager algorithm can be found at [66]. The orders stem from the work on TLRW by Dice et. al [25]. They give a detailed account of critical orders which we use here.

During the process of defining orders for each algorithm we also had to find and remove existing fences to prevent duplication. On closer inspection of the code for the store-store order in the rollback procedure of ByteEager we were unable to find any mechanism that might enforce the order.

We contacted the original authors to verify our findings. It became clear that they had built the algorithm for architectures where the order was automatically enforced, namely TSO, and they agreed a fence was necessary. We placed a dmb st fence after the source of the order to establish a baseline for comparison, noting that an order definition would have made our communication unnecessary.

|          |                                  | x86       | ARM7      |

|----------|----------------------------------|-----------|-----------|

| Dekker   | $8 \xrightarrow{W,R} 9$          | 8:mfence  | 8:dmb st  |

|          | $13 \xrightarrow{\text{W,R}} 9$  | 13:mfence | 13:dmb st |

|          | $25 \xrightarrow{\text{W,R}} 26$ | 25:mfence | 25:dmb st |

|          | $30 \xrightarrow{\text{W,R}} 26$ | 30:mfence | 30:dmb st |

|          |                                  |           |           |

| Lamport  | $8 \xrightarrow{W,R} 9$          | 8:mfence  | 8:dmb st  |

|          | $14 \xrightarrow{\text{W,R}} 15$ | 14:mfence | 14:dmb st |

|          | $31 \xrightarrow{\text{W,R}} 32$ | 31:mfence | 31:dmb st |

|          | $37 \xrightarrow{\text{W,R}} 38$ | 37:mfence | 37:dmb st |

|          |                                  |           |           |

| Parker   | $44 \xrightarrow{\text{W,*}} 46$ | 44:mfence | 44:dmb st |

|          |                                  |           |           |

| Peterson | $5 \xrightarrow{\text{W,R}} 7$   | 5:mfence  | 5:dmb st  |

|          | $14 \xrightarrow{\text{W,R}} 16$ | 14:mfence | 14:dmb st |

Figure 2.6: Orders and fences for four classic algorithms

**Difficulty** The only algorithm without orders already defined in some form was Lamport's mutex. Every other algorithm had research, implementation notes, or existing fences from which orders could be derived. We think this means execution order definition is already implicitly taking place during algorithm design but the information is lost as fence placements during implementation.

Further, in the case of ByteEager's rollback procedure, we believe that the speed with which the ByteEager authors were able to diagnose the issue suggests that authors and designers will have relatively little difficulty in defining execution orders during algorithm design.

| TL2       | LOC | Nodes |

|-----------|-----|-------|

| TxLoad    | 75  | 171   |

| TxStore   | 121 | 236   |

| TxCommit  | 277 | 398   |

|           |     |       |

| ByteEager | LOC | Nodes |

| read_ro   | 30  | 64    |

| read_rw   | 32  | 73    |

| write_ro  | 31  | 93    |

| write_rw  | 36  | 122   |

| rollback  | 25  | 93    |

Figure 2.7: Algorithm Procedure Size

### 2.4.2 Parry's Execution Time

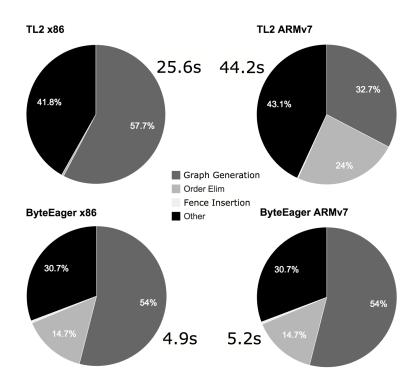

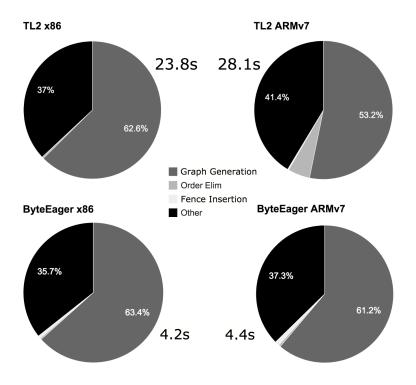

Figures 2.8 and 2.9 show the wall clock time that Parry's top-level run procedure takes to insert fences for the TL2 and ByteEager TM algorithms. Figure 2.8 shows results where the exponential order elimination algorithm was used and Figure 2.9 shows results for the linear order elimination algorithm. Notably, the elimination results from the exponential time and linear time order elimination algorithms are identical for all of the evaluated code.

The times were recorded from each stage of Parry's execution, averaged across 100 runs on an Intel Core i5 at 2.4 Ghz with 6GB of RAM with a fully updated version of Ubuntu 14.04 Server.

We include only the TM algorithms here because they are the most complex examples in our evaluation. The size of each procedure for both algorithms in lines of code and control flow graph notes is included in Figure 2.7. The lines of code are recorded without account for inlining except in the case of TL2:TxCommit where the majority of the instructions are inlined from a procedure call. The largest case is TL2:TxCommit procedure where the control-flow graph has 398 nodes. We have not included TL2 Eager since the size and times were similar to those of regular TL2.

The control-flow graph generation and order elimination account for the majority of the execution time. In the cases where the linear order elimination algorithm is used the graph generation dominates the other parts of our approach. The long execution times for graph generation are caused by a large amount of string manipulation and scanning while working with the LLVM IR in Python. The fence insertion which uses GLPK to run our integer linear program takes little time.

When executing on TL2 for x86 no time is spent on the ILP and a small amount on order elimination. Parry can forgo running the linear program entirely because all of the orders are eliminated. The order elimination only requires a small amount of time because it is immediate for orders where the source and sink instructions exist in an architecture enforced relationship.

# 2.4.3 Experiments with the Four Classic Algorithms

For the four classic algorithms, Parry inserted the fences shown in Figure 2.6. Notice that each order led to one fence. In each case, the fence is correctly placed and is the best fence possible. We note that Lamport's mutex has two "loops" due to jumps to the start of the algorithm; Parry places a fence directly after the first branch, which is a good choice.

### 2.4.4 Transactional Memory Algorithms

For the three TM algorithms, Parry inserted the fences shown in Figure 2.10 and Figure 2.13. We have an opportunity to compare those fences with a baseline. The original authors of the transactional memory algorithms inserted fences or fence macros for particular architectures, which we assume are correct for the intended architectures. From those fence placements, the literature, and in some cases consultation with the original authors, we constructed a baseline for each of x86 and ARMv7. Effectively, we acted as an implementer who selects fences; for example, for TL2 we defined an existing fence macro called MEMBARSTLD as mfence on x86. Similarly, ByteEager uses a memory fence macro WBR and the implicit memory barrier defined by the semantics of the \_\_\_sync\_\* compiler built-ins [1]. One goal of our experiments is to evaluate whether our order definitions and Parry can match the baseline. In the following subsections, we will give a detailed

comparison of both the fence placements and of the resulting performance of the TM algorithms on standard benchmarks.

# 2.4.5 Impact of Order Elimination

Figure 2.10 shows that for TL2 on x86, Parry eliminated all 7 orders and inserted no fences at all, while on ARMv7, Parry eliminated no orders. Additionally, Figure 2.10 shows that for TL2 Eager on x86, Parry eliminated all 4 orders and inserted no fences at all, while on ARMv7, Parry eliminated one order. Finally, Figure 2.13 shows that for ByteEager on x86, Parry eliminated one order, while on ARMv7, Parry eliminated no orders.

Now let us compare with the baseline. We ask: (1) are there cases where order elimination is necessary to approximate the fence placements from a knowledgeable implementor and (2) can we avoid adding fences altogether using information from the compiler? Our comparison suggests the answer is *yes* in both cases, as we will detail now.

Order elimination prevents the addition of extra fences where the architecture directly enforces an order and an implementer will never insert a fence. For example, load-load orders are automatically enforced on x86. In such cases we can establish a derivation by instantiating an architecture axiom directly and then eliminate the corresponding order. There are also situations like the write procedure for ByteEager where accounting for the cmpxchg instruction prevents the insertion of an additional fence.

Additionally, we have exhibited two instances where fences would likely be inserted by an implementer but which actually require no fence. If TL2 is compiled with the TL2\_EAGER flag, one fence in TxCommit can be eliminated on architectures like ARMv7 since the source of the order will not appear in the control flow graph. If TL2 is compiled by Clang on x86, another fence can be eliminated in TxCommit due to generated instructions which allow for a transitive order derivation. In these cases a detailed accounting of the control flow graph is important in determining whether an order is already enforced.

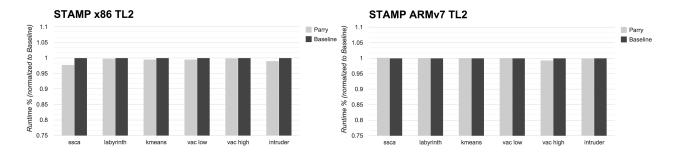

#### 2.4.6 Performance Benchmarks

We compare the performance of Parry's output with the baseline using six of the benchmarks from the STAMP benchmark suite v0.9.10 [64] which is designed for testing transactional memory algorithms. We ran the x86 benchmarks on an Intel Core i5 at 2.4 Ghz with 6GB of RAM with a fully updated version of Ubuntu 14.04 Server. The ARMv7 benchmarks were run on an Exynos 5 Dual at 1.7Ghz with 2GB of RAM with the same operating system.

We compiled the results of each benchmark by taking the arithmetic mean of each over 100 runs and then recording the percentage difference between the baseline version and the Parry version.

Importantly everything was compiled with Clang version 3.3. This is the same version used in Parry to generate IR, control flow graphs. Using the same version of Clang to generate the control flow graphs and to compile the algorithms ensures that the assertions we make about the graphs remain valid for the final compiled output.

### 2.4.7 TL2 and TL2 Eager Measurements

Figure 2.10 shows the fences inserted by Parry alongside the fences placed in the baseline. We associate them by the orders we defined for TL2. For example the last two orders for TL2 correspond with the orders from our running example, TxCommit. All of the orders were accounted for by fence macros. This is not surprising given that the authors would have a deep understanding of the algorithm's behavior under weak memory models.

The orders are defined using line numbers which can be referenced in the code which accompanies our project [11]. We have included annotations for the instruction types that should be ordered when they appear in the intermediate representation. For example the order between lines 760 and 1413 in TxCommit is a store-store order between the store of a value in the write-set and a store to release the lock for the write-set's address. In this case the line numbers appear to be abnormally distant from one another but, due to procedure inlining, they both appear in the control flow graph for TxCommit. We have also included a mapping from the orders in our running example to the line number orders in Figure 2.11.

Figure 2.8: Parry Execution Times, Full Order Elimination

Figure 2.9: Parry Execution Times, Linear Elimination

| TL2                                  |             | x86        |                   | ARM7             |

|--------------------------------------|-------------|------------|-------------------|------------------|

| TxLoad                               | baseline    | ours       | baseline          | ours             |

| $2078 \xrightarrow{R,R} 2080$        | _           | _          | 2078:dmb          | 2078:dmb         |

| $2080 \xrightarrow{R,R} 2082$        | _           | _          | 2080:dmb          | 2080:dmb         |